SPI (Serial Peripheral interface) 串口外围设备接口

SPI 是一种高速,全双工,同步的通信总线。

优缺点

-

优点

-

缺点

- 没有制定的流控制,没有应答机制确认是否接收到数据,所以肯靠性有一定的缺陷

特点

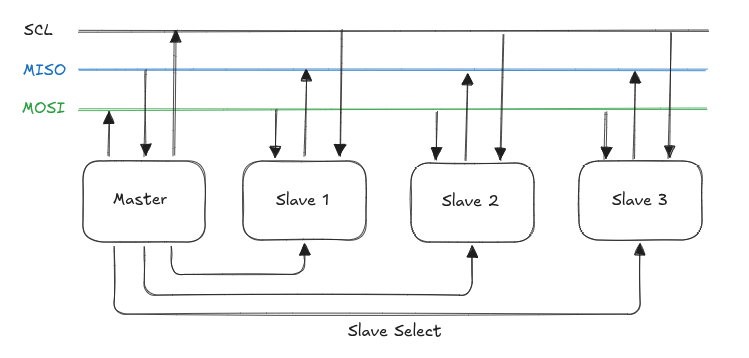

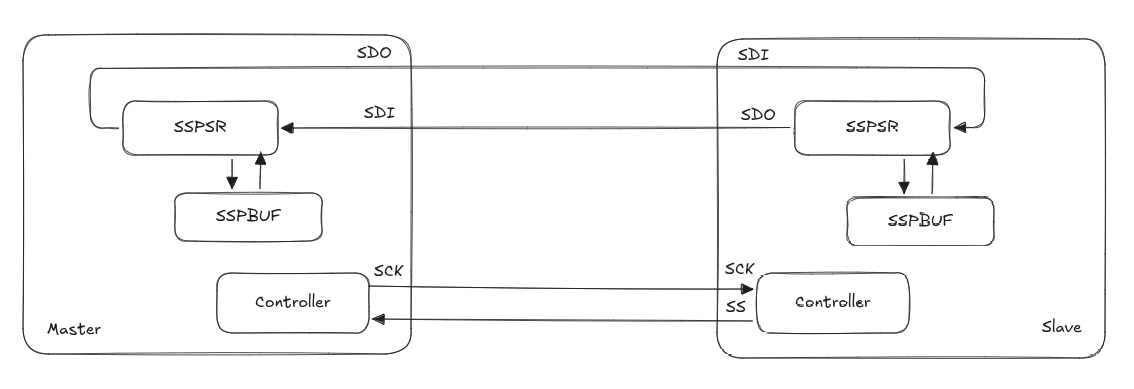

- 采用主从模式(Master-Slave)的控制方式

SPI规定两个SPI设备之间通信必须由主设备来控制次设备。一个Master设备可以通过提供Clock以及对Slave设备进行片选来控制多个slave设备。

始终信号通过时钟极性(CPOL)和时钟相位(CPHA)控制着两个SPI设备间交换数据和采样的时间,保证两个设备之间是同步传输的。

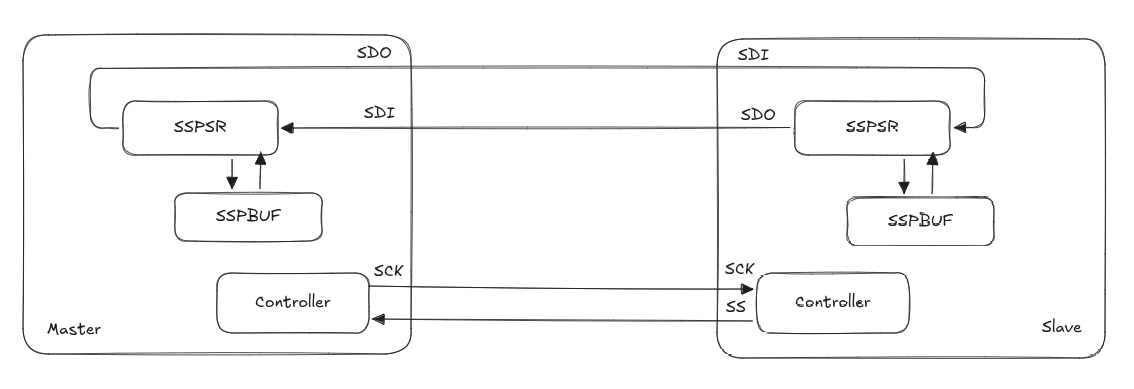

SPI没有数据读和写的说法,在每个Clock周期内,SPI设备都会发送并接受一个bit大小的数据。相当与该设备有一个bit大小的数据被交换了。

因此,发送一个数据必然会收到一个数据;接收数据必须先发送一个数据。

工作机制

管脚

SPI相关说法

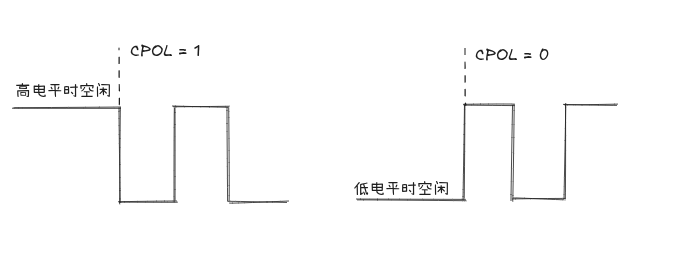

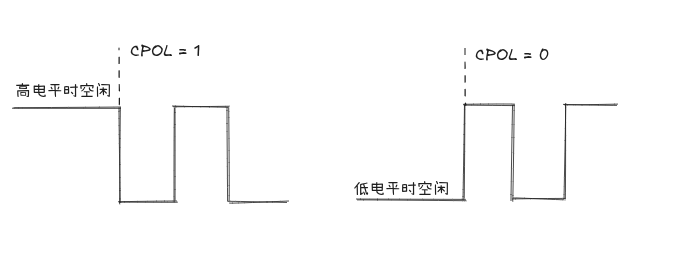

(时钟)极性: 直接影响SPI总线空闲时是高电平还是低电平

-

CPOL = 1; 空闲时为高电平

-

CPOL = 0; 空闲时为低电平

SPI总线的相位

-

CPHA = 0; 从第一个跳变沿开始采样

-

CPHA = 1; 从第二个跳变沿开始采样

SPI传输的四种模式

| mode |

CPOL |

CPHA |

| mode 0 |

0 |

0 |

| mode 1 |

0 |

1 |

| mode 2 |

1 |

0 |

| mode 3 |

1 |

1 |

-

CPOL=0,CPHA=0:此时空闲态时SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

-

CPOL=0,CPHA=1:此时空闲态时SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

-

CPOL=1,CPHA=0:此时空闲态时SCLK处于高电平,数据采集是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

-

CPOL=1,CPHA=1:此时空闲态时SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。